ISSN: 2089-3272, DOI: 10.11591/ijeei.v9i1.1706

# Design of the Digital I/O Pad Buffer for Mixed-Voltage Application

## Said El Mouzouade<sup>1</sup>, Karim El khadiri<sup>2</sup>, Zakia Lakhliai<sup>3</sup>, Ahmed Tahiri<sup>4</sup>

1.2.3.4Laboratory of Computer Science and Interdisciplinary Physics (L.I.P.I), Normal Superior School Fez (E.N.S.F) Sidi Mohamed Ben Abdellah University, Fez, Morocco

## **Article Info**

# Article history:

Received Oct 14, 2019 Revised Feb 26, 2021 Accepted Mar 9, 2021

## .Keywords:

Mixed-voltage Digital I/O Pad Bi-direction I/O

#### **ABSTRACT**

A new circuit design of digital bidirectional input/output (I/O) pad buffer for mixed voltage is presented. The digictal bidirectional I/O buffer is designed to avoid reflections by matching the output impedance to the 50 ohms of the transmission line and having overshoots and undershoots below 300mV by increasing the output impedance. The digital bidirectional I/O pad buffer provides minimum delays between input and output and minimum rising and falling times. The proposed digital bidirectional I/O pad buffer was designed, simulated and layouted in Cadence using in TSMC 0.18um CMOS process with a linear resistive element electrically connected at an I/O pad for limiting a processed data I/O signal. The output rising time and falling time are 0.42 ns and 0.93 ns with 3pF load respectively. The final chip area is only 5 um<sup>2</sup>

Copyright © 2021 Institute of Advanced Engineering and Science.

All rights reserved.

62

## Corresponding Author:

## Said El Mouzouade,

Laboratory of Computer Science and Interdisciplinary Physics (L.I.P.I), Normal Superior School Fez (E.N.S.F), Sidi Mohamed Ben Abdellah University, B.P 5206 Bensouda- ENS, Fez, Morocco.

Email: said.elmouzouade@usmba.ac.ma

## 1. INTRODUCTION

To reduce the silicon cost, to increase circuit performance and high speed operating. The dimension of transistors has been scaled down towards the nanometer region, and the power supply voltage has also decreased [1]. However, it is hard for system design to convert all high voltage components into low voltage integrated circuits due to the cost consideration. Therefore, many microelectronic systems often require internal integrated circuit components to be designed with a mixed-voltage interface [2]. For example, a chip that operates with 1.8V internal power supply voltage may receive signals of 3.3V from external components, so you have to design mixed-voltage I/O buffers for the 1.8V chip. Although mixed-voltage I/O buffers have overcome several problems, such as gate-to-oxide reliability [3], due to the high electric field resulting from the high voltage difference between the gate-drain and gate-source terminals, degradation of hot carriers [4], occurs when the drain-source voltage of the transistor operating in saturation mode is greater than the normal operating voltage. Undesired circuit leakage paths [5] occur from the I/O pad to the power supply voltage through this parasitic PN-Junction diode.

To overcome these problems, several mixed voltage I / O buffers have been proposed. To avoid the problem of the reliability of oxide carriers, a mixed voltage I / O buffer with an NMOS blocking technique has been proposed [6]. But, operating in the ultra-low voltage region, the use of these techniques can limit the voltage oscillation of the received inputs, degrading the reception speed. In [7], special polarization techniques can be used to prevent degradation of hot carriers. To eliminate unwanted circuit leakage paths, a mixed voltage I/O buffer adopting gate voltage tracking and dynamic n-well bias techniques has been proposed [8]. However, the buffer requires many additional transistors having complicated connections, resulting in increased design cost and area of layout. In this article, a new digital I/O buffer circuit design is proposed to provide a small area, to avoid reflections, minimum delays between input and output, minimum rise and fall times, and overshoots and undershoots of less than 300 mV.

IJEEI ISSN: 2089-3272  $\square$  63

#### 2. PROPOSED DIGITAL I/O PAD BUFFER

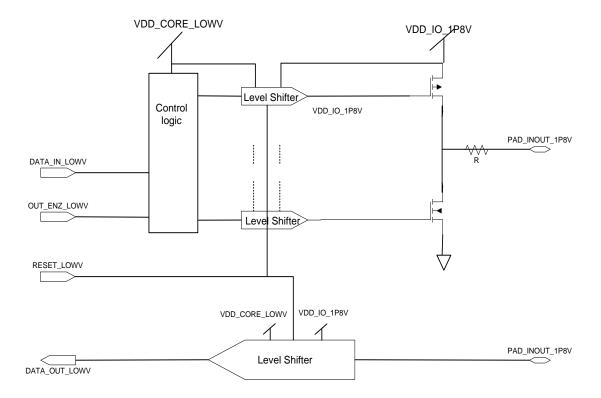

The block diagram of the proposed digital I/O pad buffer is shown in Figure 1. The output stage is the same for the two digital I/O pad buffers.

Figure 1. The block diagram of the proposed Digital I/O pad buffer

The proposed digital I/O pad buffer consists of two parts; input part and output part. The input part is composed of a schmitt trigger and inverter control logic. The output part comprises a logic control, a PMOS driver, a NMOS driver, an output stage and a linear resistive element electrically connected at an I/O pad for limiting a processed data I/O signal. The digital I/O buffer controls I/O output impedance using a combination of FET pull-up and pull-down in series with a linear resistive element. The pull-up and pull-down stages include the respective PMOS driver and NMOS driver, which are controlled by a logical circuit.

The logical control utilizes these signals to generate logical signals to control the PMOS driver and NMOS driver. The PMOS driver and NMOS driver, therefore, control the output stage. It is this controlled active output impedance in series with a fixed linear resistive element.

The linear resistive R may be configured to provide a significant portion of the pad output impedance. The trade-off to design the output impedance of the buffer:

- To have an output impedance as close as possible to the 50 ohms of the transmission line, avoid reflections

- To be large enough to minimize the delays between input and output are requested, need to reduce the output impedance

- To have overshoots and undershoots below 300mV, need to increase the output impedance

- To have relative small rising and falling times, need to reduce the output impedance

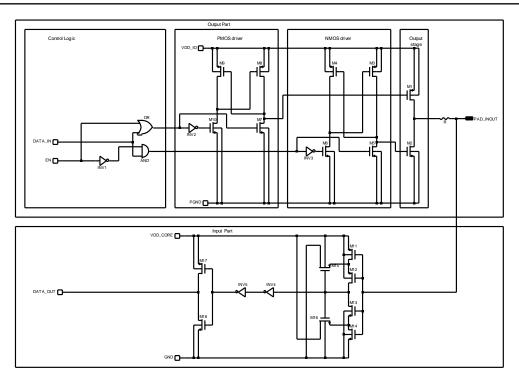

The proposed design concept of digital bidirectional I/O buffer is shown in Figure 2. The design was carried out according to the following priority; Increase the output impedance as much as possible by reducing the size of the PMOS and NMOS output to meet the specification of input to output delay, and to meet the specification of rise and fall times, and to obtain a higher output impedance and as close as possible to 50 ohms. And check that the overshoots and undershoots do not exceed 300mV.

64 □ ISSN: 2089-3272

Figure 2. The proposed design concept of digital bidirectional I/O buffer

# 3. SIMULATION AND RESULTS

The design of the digital I/O pad buffer has been implemented in TSMC 180 nm CMOS technology. The digital pad buffer is characterized using ACS with:

- Statistical Models (No Matching)

- Corner Models (Nmos= weak or strong, Pmos= weak or strong)

The electrical simulations for the output stage take into account:

- Layout parameters

- ESD structure used

- Package Models

- Lines specifications.

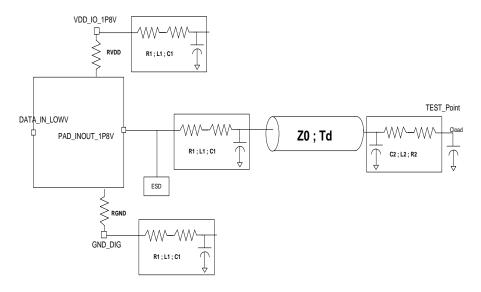

As shown in Figure 3, the following block diagram gives the test bench to be used for electrical simulations:

## Figure.3. Block diagram for electrical simulations

# 3.1. Layout of the Digital I/O pad buffer proposed

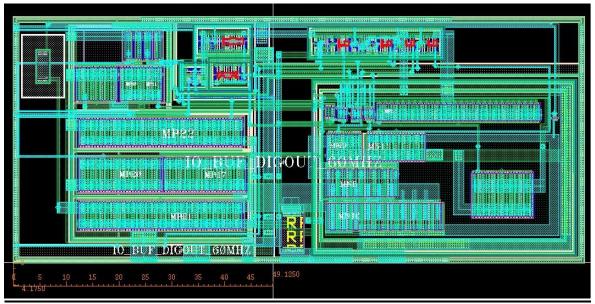

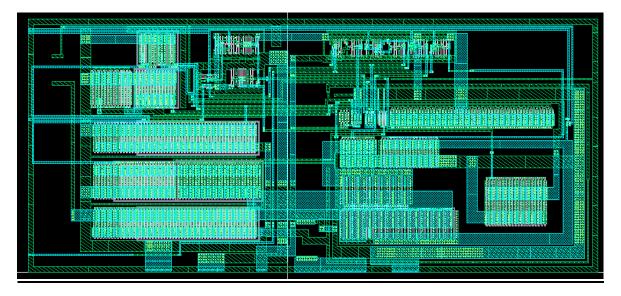

The layout and extracted of the proposed digital I/O pad buffer are shown in Figures 4 and 5. All devices or circuits prone to produce electromagnetic interference or susceptible to interference are enclosed with double-layer guard rings. The layout is done by respecting the following items; design rules (DRM, MRC, and Density) and designer constraints information (constraint manager, matchCat...) and use only metal1, metal2, and Metal-6 layer are not used. We choose the coupled model for the extracted (Assura RCX, R-C model) because it gives worst results than the de-coupled (reference=GND\_DIG) model. The total area of the proposed circuit in TSMC 180 nm technology is 0.005 mm<sup>2</sup>.

Figure 4. The layout of the proposed digital I/O pad buffer

Figure 5. The extracted of the proposed digital I/O pad buffer

#### 3.2. Post-Layout Characterization using ACS

Post-layout simulation is very useful to modify the designed digital I/O pad buffer and become closer to the measurement specifications. The proposed digital I/O pad buffer has been post-layout simulated using Cadence Virtuoso with drawing layout and checking DRC and LVS. The corner processes analysis is reported to demonstrate the mismatch and global process variations on the transient response of the proposed digital I/O pad buffer.

66 □ ISSN: 2089-3272

We plot the weak, strong, and typical output curves for each application case, line parameters, and the input curve. The corners are defined as described in the table 1 below:

| TD 11 1 | 1 10 0 1      | . 1           | C .1    | 1 .    |

|---------|---------------|---------------|---------|--------|

| Table   | l llatinad    | the corners   | Of the  | damea  |

| I ainc  | ı . 170111100 | . uic coincis | OI LIIC | ucvicc |

| Corner  | NMOS   | PMOS   | RESISTOR | Routing<br>Resistor | Supplies | TEMP<br>(deg) |

|---------|--------|--------|----------|---------------------|----------|---------------|

| "Typic" | typic  | typic  | typic    | nom                 | nom      | 27            |

| "Weak"  | weak   | weak   | high     | max                 | min      | 125           |

| "Srong" | strong | strong | low      | min                 | max      | -40           |

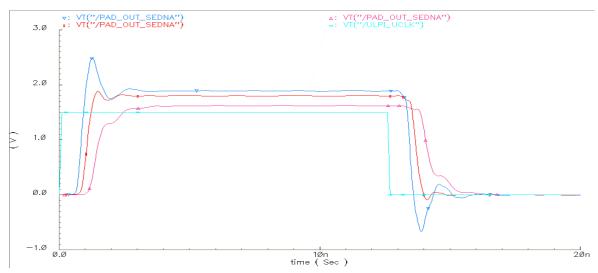

# a) One chip connected – High drive = '1' with Z0=44ohm, Td=112p

Figure 6 shows the curve voltage for Rising/Falling edge of the proposed digital I/O pad buffer. With one chip connected – High drive = '1' with  $Z_0=440$ hm,  $Z_0=44$ hm,  $Z_$

Figure 6. Curve for Rising/Falling edge

Table 2 shows the AC characteristics of the proposed digital I/O pad buffer for Rising/ Falling edge. The delay times are simultated from the input signal (VIO) of 0.9 voltage level to the output signal (PAD) of 1.8 voltage level. As shown in Table 1, the simulated rising delay time Trise-rising are 0.42 ns with 3 pF load. The falling delay time Tfalle-falling are 0.93 ns with 3pF load. The output rising time Trisie and falling time Tfalle are defined from output rise time on test point 10%-90% and from output fall time on test point 10%-90%, respectively. As shown in Table 1, the simulated delay rising (Delay\_r) are 0.93 ns with 3 pF loads. The delay falling (Delay\_f) are 0.95 ns with 3 pF loads. The duty cycle D cycle is defined the pulse duration from test point 10%-90% at rise edge of the output signal (PAD) to test point 10%-90% at fall edge divided by the period of the output signal (PAD). As shown in Table 1, the simulated Dcycle are 50.9% under the load 3 pF.

Table 2. AC characteristics simulated of the digital I/O pad buffer for Rising/ Falling edge

| Parameter  | Description                                             | Min  | Nom  | Max  | Units |

|------------|---------------------------------------------------------|------|------|------|-------|

| Freq       | Input Frequency                                         |      |      | 40   | □Hhz  |

| Trise      | Output Rise Time on Test Point 10%-90%                  | 0.28 | 0.42 | 1.58 | ns    |

| Tfall      | Output Fall Time onTest Point 10%-90%                   | 0.24 | 0.38 | 1.54 | ns    |

| Delay_r    | Internal rise delay between IN_LOWV and Test Point - Td | 0.73 | 0.93 | 1.27 | ns    |

| Delay_f    | Internal fall delay between DATA_IN_LOWV and Test Point | 0.73 | 0.95 | 1.33 | ns    |

| Overshoot  | Maximum Overshoot on PAD and Test Point                 |      | 13   | 326  | mV    |

| Undershoot | Maximum Undershoot on PAD and Test Point                |      | 23   | 421  | mV    |

| Duty Cycle | Duty cycle on test point                                | 49.9 | 50.4 | 50.9 | %     |

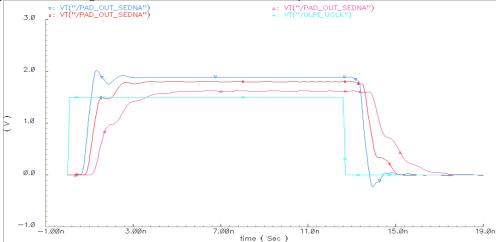

b) One chip connected – High drive =' 0' with Z0=80ohm, Td=112p.

Figure 7 shows the curve voltage for Rising/ Falling edge of the proposed digital I/O pad buffer. With one chip connected – High drive =' 0' with Z0=80ohm, Td=112p.

Figure 7. Curve for Rising/Falling edge

Table 3 shows the AC characteristics of the proposed digital I/O pad buffer for Rising/ Falling edge. The delay times are simultated from the input signal (VIO) of 0.9 voltage level to the output signal (PAD) of 1.8 voltage level. As shown in Table 1, the simulated rising delay time Trise-rising are 1.57 ns with 3 pF load. The falling delay time Tfalle-falling are 0.65 ns with 3pF load. The output rising time Trisie and falling time Tfalle are defined from output rise time on test point 10%-90% and from output fall time on test point 10%-90%, respectively. As shown in Table 1, the simulated delay rising (Delay\_r) are 1.09 ns with 3 pF loads. The delay falling (Delay\_f) are 1.12 ns with 3 pF loads. The duty cycle D cycle is defined the pulse duration from test point 10%-90% at rise edge of the output signal (PAD) to test point 10%-90% at fall edge divided by the period of the output signal (PAD). As shown in Table 1, the simulated Dcycle are 51.2% under the load 3 pF.

Table 3. AC characteristics simulated of the digital I/O pad buffer for Rising/Falling edge

| Parameter  | Description                                             | Min  | Nom  | Max  | Units |

|------------|---------------------------------------------------------|------|------|------|-------|

| Freq       | Input Frequency                                         |      |      | 40   | □Hhz  |

| Trise      | Output Rise Time on Test Point 10%-90%                  | 0.42 | 1.57 | 2.17 | ns    |

| Tfall      | Output Fall Time onTest Point 10%-90%                   | 0.39 | 0.65 | 2.09 | ns    |

| Delay_r    | Internal rise delay between IN_LOWV and Test Point      | 0.81 | 1.09 | 1.56 | ns    |

| Delay_f    | Internal fall delay between DATA_IN_LOWV and Test Point | 0.80 | 1.12 | 1.69 | ns    |

| Overshoot  | Maximum Overshoot on PAD and Test Point                 |      | 14   | 308  | mV    |

| Undershoot | Maximum Undershoot on PAD and Test Point                |      | 24   | 488  | mV    |

| Duty Cycle | Duty cycle on test point                                | 49.9 | 50.5 | 51.2 | %     |

## 3.3. Characterization of Current Consumptions (Reset Mode and Active mode)

The Characterizations of Current Consumptions (Reset Mode and Active mode) are shown in Tables 4 and 5.

## a) Reset Mode

Table 4 shows that the current consumption in reset mode is less than 90 nA without a clock input.

Table 4. Characterization of Current Consumptions for Rest Mode

| Parameter                   | Conditions          | Nom | Max  | Unit |  |

|-----------------------------|---------------------|-----|------|------|--|

| V <sub>DD</sub> _CORE_LOWV  | Without Clock input | 0.3 | 30.0 | nA   |  |

| $V_{DD}\_IO\_LOWV = V_{IO}$ | Without Clock input | 0.3 | 30.0 | nA   |  |

| $V_{DD}\_IO\_LOWV = V_{IO}$ | Without Clock input | 2.9 | 90.0 | nA   |  |

68 ISSN: 2089-3272

## b) Active Mode (High drive =' 0')

It is clear from Table 5 that the current consumptions for the active mode are less than 756 nA with clock running @40Mhz.

Table 5. Characterization of Current Consumptions for Active Mode

| Parameter                   | Conditions                | Conditions Nom Ma |       | Unit |

|-----------------------------|---------------------------|-------------------|-------|------|

| V <sub>DD</sub> _CORE_LOWV  | With Clock running @40Mhz | 64.5              | 79.1  | nA   |

| $V_{DD}\_IO\_LOWV = V_{IO}$ | With Clock running @40Mhz | 0.01              | 0.87  | nA   |

| $V_{DD}\_IO\_LOWV = V_{IO}$ | With Clock running @40Mhz | 609.7             | 756.0 | nA   |

Table 6 tabulates the comparison with several prior works. The proposed design of digital bidirectional input/output (I/O) pad buffer for mixed voltage uses the least number of devices and possesses.

Table 6. Performance Comparison of input/output (I/O) pad buffer

| Parameter          | [9]    | [10]  | [11]   | This work |

|--------------------|--------|-------|--------|-----------|

| Year               | 2016   | 2018  | 2019   | 2021      |

| Process            | 130 nm | 180n  | 180 nm | 180 nm    |

| VDD (V)            | 1.2    | 1.8   | 1.8    | 1.8       |

| Delay falling (ns) | >100   | 31.7  | 4.81   | 0.93      |

| Delay rising(ns)   | >200   | 1.78  | 5.19   | 0.95      |

| Duty Cycle(%)      | -      | -     | 48.3   | 51.2      |

| Freq (Mhz)         | -      | -     | -      | 40        |

| Area (µm2)         | -      | 108.8 | -      | 5         |

## 4. CONCLUSION

In this paper, a novel design of digital bidirectional input/output (I/O) pad buffer for mixed voltage is proposed and evaluated. The proposed I/O buffer provides lower latency and a smaller layout area than conventional I/O buffers. The conventional and proposed mixed-voltage I/O buffers are designed in a 180-nm CMOS process, whose evaluation results indicate that the proposed I/O buffer achieves up to 50% reduction on propagation delay. They also indicate that the proposed I/O buffer achieves up to 40% reduction on silicon area as compared to conventional mixed-voltage I/O buffers. Several applications are implemented using the designed circuit and post layout simulation show promising results. The output rising time and falling time are 0.42 ns and 0.93 ns with 3pF load respectively. The final chip area is only 5 um². The presented design procedure is suitable for use in portable applications like the Internet of Things (IoT).

#### ACKNOWLEDGMENTS

This work was supported by the National Center for Scientific and Technical Research (CNRST Morocco) under the PPR2 program.

#### REFERENCES

- [1] Ker, M.D., et al.: "Overview and design of mixed-voltage I/O buffers with low-voltage thin-oxide CMOS transistors", *IEEE TCAS-I 53(9)*, 1934–1945, 2006.

- [2] Ker, M.D., et al., "Design of mixed-voltage I/O buffer by using NMOS-blocking technique", IEEE JSSC 41(10), 2324–2333, 2006.

- [3] Ker, M.D., et al., "Design on mixed-voltage I/O buffers with consideration of hot-carrier reliability", In: *International Symposium on VLSI Design, Automation and Test*, pp. 1–4, 2007

- [4] T. Furukawa, D. Turner, S. Mittl, M. Maloney, R. Serafin, W. Clark, L. Longenbach, and J. Howard, "Accelerated gate-oxide breakdown in mixed-voltage I/O buffers", in Proc. *IEEE Int. Reliability Physics Symp.*, pp. 169–173, 1997.

- [5] I.-C. Chen, J. Y. Choi, and C. Hu, "The effect of channel hot-carrier stressing on gate-oxide integrity in MOSFETs", *IEEE Trans. Electron Devices*, vol. 35, pp. 2253-2258, 1988.

- [6] S. Voldman, "ESD protection in a mixed voltage interface and multrial disconnected power grid environment in 0.5- and 0.25-μm channel length CMOS technologies", in *Proc. EOS/ESD Symp.*, pp. 125-134, 1994.

- [7] M.-D. Ker, S.-L. Chen, and C.-S. Tsai, "Overview and design of mixed-voltage I/O buffers with low-voltage thinoxide CMOS transistors", *IEEE Trans. on Circuits and Systems* I, vol. 53, no. 9, pp. 1934-1945, 2006.

- [8] A.-J. Annema, G. J. G. M. Geelen, and P. C. de Jong, "5.5- V I/O in a 2.5-V 0.25-μm CMOS Technology", *IEEE J. Solid-State Circuits*, vol. 36, no.3, 2001.

- [9] Y. Huang, A. Shrivastava, L. E. Barnes, and B. E. Calhoun, "A design and theoretical analysis of a 145 mv to 1.2 v single-ended level converter circuit for ultra-low power low voltage ics", *Journal of Low Power Electronics and Applications*, vol. 6, no. 3, pp. 11:1–14, 2016.

- [10] M. Lanuzza, F. Crupi, S. Rao, R. D. Rose, S. Strangio, and G. Iannaccone, "An ultralow-voltage energy-efficient level shifter," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 64, no. 1, pp. 61–65, January 2017

- [11] F. Peng," An output buffer for 5 V applications in a 0.18 lm 1.8 V/3.3 V CMOS process", *Integrated Ferroelectrics*, vol. 198, pp. 153-159, 2019.

# **BIOGRAPHY OF AUTHORS**

Said El Mouzouade received his master's degree in Microelectronics from faculty of sciences Dhar EL Mahraz Fez Morocco in 2012. He is now PhD student in the Laboratory of Computer Science and Interdisciplinary Physics (L.I.P.I), Normal Superior School Fez (ENSF) Sidi Mohamed Ben Abdellah University, Fez, Morocco. His current research interests include power management circuits and systems, switched-inductor and switched-capacitor power converters, low dropout regulators, wireless power transfer for Internet of Things (IoT), and analog IC design methodologies.

**Karim El Khadiri** received the master's and Ph.D.degree in electrical engineering and computers from the Department of physics, faculty of sciences Dhar EL Mahraz Fez, Sidi Mohamed Ben Abdellah University Morocco in 2012, and 2017, respectively.

In 2019, he joined the Laboratory of Computer Science and Interdisciplinary Physics (L.I.P.I), Normal Superior School Fez (ENSF) Sidi Mohamed Ben Abdellah University, Fez, Morocco, where he is currently an Associate Professor and guest researcher at LIMA laboratory in UQO Canada. His current interests include a switch-mode audio amplifier, CMOS mixed-mode integrated circuit design, designs techniques for RFID, RF front-ends for passive tags, Li-Ion battery charger, and power management.

Zakia Lakhliai received the Ph.D. degree in physics from the University of Montpellier II, France, in 1987, and the State Doctor's degree from the University of Fes, Morocco, in 1996. She is currently a member of Lab of computering and interdisciplinary physics (L.I.P.I), at (E.N.S.F), and a Professor in the Superior School of technology (E.S.T.F.) at Sidi Mohammed Ben Abdellah University (USMBA), Fez, Morocco. Her current research interests signal and image processing, analog and mixed integrated circuits.

Ahmed Tahiri received the graduate degree DES in Department of Physics, Sidi Mohammed Ben Abdellah University, Morocco in 1997, received the Ph.D. degree in physics from the University Sidi Mohamed Ben Abdellah, Faculty of Science, Morocco in 2005. He completed his doctoral studies in didactics of science in the University of Sherbrooke in Canada in 2010. He is now a professor in Normal Superior School, ENS-FEZ, Morocco. His research interests include image processing, computer science and didactics of scientific disciplines.